ASE Flip-Chip Build-up Substrate Design Rules - ppt video online download

$ 5.50 · 4.9 (137) · In stock

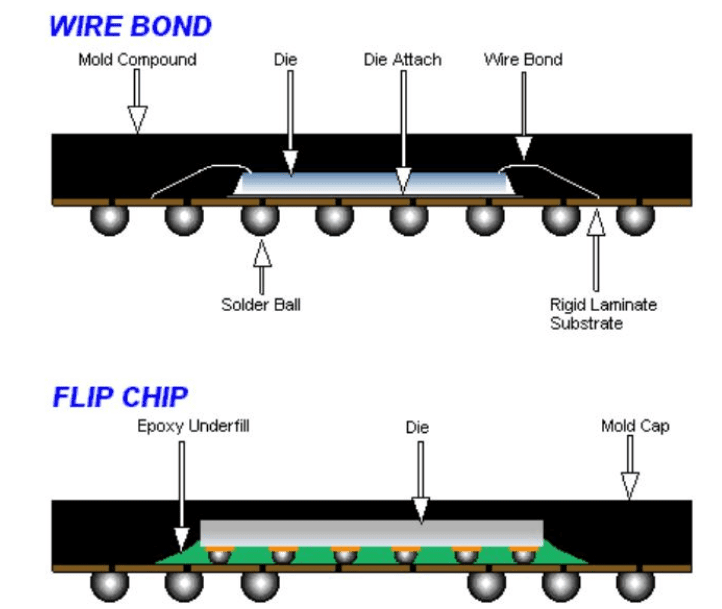

Content The Data needed for Design Build Up Flip Chip lead time Flip Chip Pad Design Rule Fine Flip Chip Pitch Proposal – 200 / 150 um Layout Rule for Build Up Layer Layout Rule for Core Layer Available Substrate Structure Assembly Rule Substrate Roadmap

ASE Flip-Chip Build-up Substrate Design Rules

ADVANCED. SEMICONDUCTOR. ENGINEERING, INC. ASE Flip-Chip. Build-up Substrate. Design Rules. Date : 2/12/2004 Rev. H.

Layout Rule for Build Up Layer. Layout Rule for Core Layer. Available Substrate Structure. Assembly Rule. Substrate Roadmap.

Package type & Body size. Wafer thickness & Die size. Die orientation Including Pin 1 logo, die up or die down. Die pad number, metal size & passivation opening. UBM diameter. Solder bump height, pitch & composition. Solder ball size, pitch, number, location. Net list ( net name, coordinates and ball no. ) Special Requirement (Thermal, Electrical or Others)

Flip Chip BGA 7 days >>> 5 days. Built-up Substrate 1st Article Delivery: (After Vendor drawing confirm) Lead Time General Hot-Run layers : 6.0 wk 4.5 wk layers : 6.5 wk 5.0 wk layers : 7.0 wk 5.5 wk layers : 8.0 wk 6.0 wk. For ASEMT Only: Lead Time General Hot-Run *Super Hot-Run layers : 4.0 wk 3.5 wk 3.0 wk layers : 4.5 wk 4.0 wk 3.5 wk layers : 5.0 wk 4.5 wk 4.0 wk layers : 6.0 wk 5.0 wk 4.5 wk. * Maximum 1K units (per substrate per order)

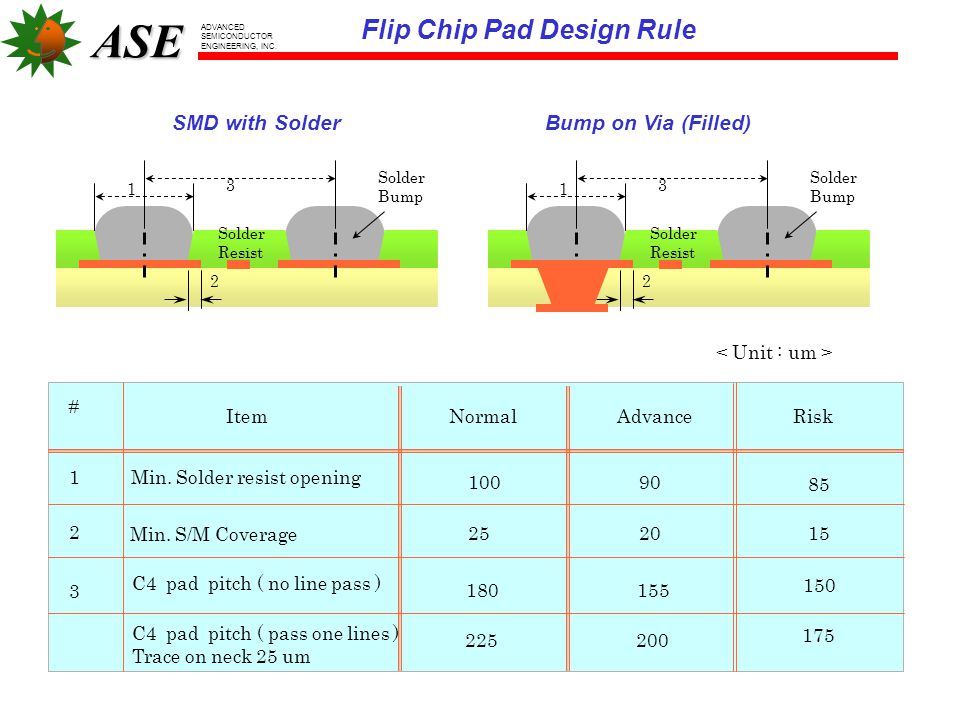

SMD with Solder. Bump on Via (Filled) Solder. Resist. Bump Solder. Resist. Bump < Unit : um > # Item. Normal. Advance. Risk. 1. Min. Solder resist opening Min. S/M Coverage C4 pad pitch ( no line pass ) C4 pad pitch ( pass one lines ) Trace on neck 25 um

**200 um Bump Pitch for One Line Pass. Solder. Resist. Bump. B. A. C. F. G.

**150 um Bump Pitch for One Line Pass. Solder. Bump. B. A. Solder. Resist. C. E. 1st layer. F. D. H. 2nd layer. G. For 150um proposal, Need to Control Die Bump UBM Diameter: 70 ~ 90 um.

C. D. E. G. H. Bump Local Area. F.

Au Plating. Build up layer. Solder resist. Solder. Number of. build up layer. 1, 2, 3, 4 / Side. 2, 4. Core layer. Layer Structure. Location. Thickness ( um ) Core substrate Core Cu. 29. Build up Cu. 15. Insulation layer. 34. Solder Resist layer. 24. Nickel plating. 3~7. Gold plating (Immersion Gold) 0.03~0.12.

UNIT: um A. B. C. G(min) C. A. B. G. Pad A. B. C. G(min) Pad A. B. C. G(min) Pad A. B. C. G(min) Pad

FC CSP. E. F. Die. B. Die. D. C. A. Peripheral bump allocation. Array bump allocation. Unit : mm. Dimension. Item. Desicription. Remark. Over molded FC CSP. Underfilled FC CSP. A. Package size. 4≦ A, B≦ ≦A, B≦ x22 is Max. rectangular package size. B. C. ≦ (A-2) ≦ (A-3) Die size. D. ≦ (B-2) ≦ (B-3) E. Bump pitch min min. By peripheral for substrate design. F. Bump pitch min min. By array for substrate design. Notes: * If it is array bump placement for Over molded FC CSP, there is a limitation for no bumps by 2x2mm area in the center of die. ** The bump pitch 315 um min. should be regarded with substrate C4 pads design. For routing concern, the design of bump pitch should be larger than 315 um for layout routing.

Attached Area. Die on the bottom. A. B. G. H. To achieve our mission, we have the following strategies: We will locate our main facilities in IC clusters with foundries to provide clients complete solutions in IC outsourcing. This also allows us to work closely with front-end service providers to develop technology and processes for the next generation of products. We will continue to grow organically as well as through strategic acquisitions. We will maintain and further enhance our leadership in offering complete semiconductor manufacturing services through technology driven solutions. We will leverage our dominance in test as it is increasingly becoming a key differentiator. Also, we will be aggressively ramping up our capacity in design and production of substrates, which are becoming a significant percentage of packaging costs and are currently controlled by a limited number of vendors.

D. E. B. C. F. Stiffener Ring. A. F. E. D. C. Chip Capacitor. Attached Area. Once-piece Metal. One-piece Metal. To achieve our mission, we have the following strategies: We will locate our main facilities in IC clusters with foundries to provide clients complete solutions in IC outsourcing. This also allows us to work closely with front-end service providers to develop technology and processes for the next generation of products. We will continue to grow organically as well as through strategic acquisitions. We will maintain and further enhance our leadership in offering complete semiconductor manufacturing services through technology driven solutions. We will leverage our dominance in test as it is increasingly becoming a key differentiator. Also, we will be aggressively ramping up our capacity in design and production of substrates, which are becoming a significant percentage of packaging costs and are currently controlled by a limited number of vendors. B

Cx1. Dy1. Dx1. Cy1. Cx3. Dy3. Dx3. Cy3. Cx2. Dy2. Dx2. Cy2. E. To achieve our mission, we have the following strategies: We will locate our main facilities in IC clusters with foundries to provide clients complete solutions in IC outsourcing. This also allows us to work closely with front-end service providers to develop technology and processes for the next generation of products. We will continue to grow organically as well as through strategic acquisitions. We will maintain and further enhance our leadership in offering complete semiconductor manufacturing services through technology driven solutions. We will leverage our dominance in test as it is increasingly becoming a key differentiator. Also, we will be aggressively ramping up our capacity in design and production of substrates, which are becoming a significant percentage of packaging costs and are currently controlled by a limited number of vendors.

SPECIAL. FIGURE. DESCRIPTION. (min) (min) REMARK. Distance between die edge. corner to the center of. fiducial mark for adding. spreader. Could be even. smaller if there is. A No heat spreader. requirement. A. If there were SMD. B. Diameter of Circle Mark component, Special. rule can’t apply. If there were SMD. C. Width of square mark component, Special. B. C. rule can’t apply. B. D. If there were SMD. D. Length of square mark component, Special. rule can’t apply. Notes: ● Each substrate should have more than two fiducial marks for flip chip process. ● Fiducial mark should be put on the outer side s of die edge corner 3 mm min. ● All the fiducial marks should be put on the diagonal location, and there must be two different fiducial mark on the diagonal location.

2. Solder Mask Opening for fiducial mark. Unit : um. SPEC. FIGURE. DESCRIPTION. TYP. SPECIAL. REMARK. (min) (min) For NSMD type C4 Pad. A. Distance of S/M to. fiducial mark C. A. B. Distance of S/M to. fiducial mark. B Distance of S/M to. fiducial mark. C Solder mask opening. For SMD (with solder) type C4 Pad. Distance of S/M to. fiducial mark. A C. A. B. Distance of S/M to. fiducial mark. B Distance of S/M to. fiducial mark. C Solder mask opening.

New Via Structure Time Line-I

New Via Structure Time Line-II

How does your Stack-up, stack up?

Message from General Chair – ICEE

Page 198 – RAYPCB

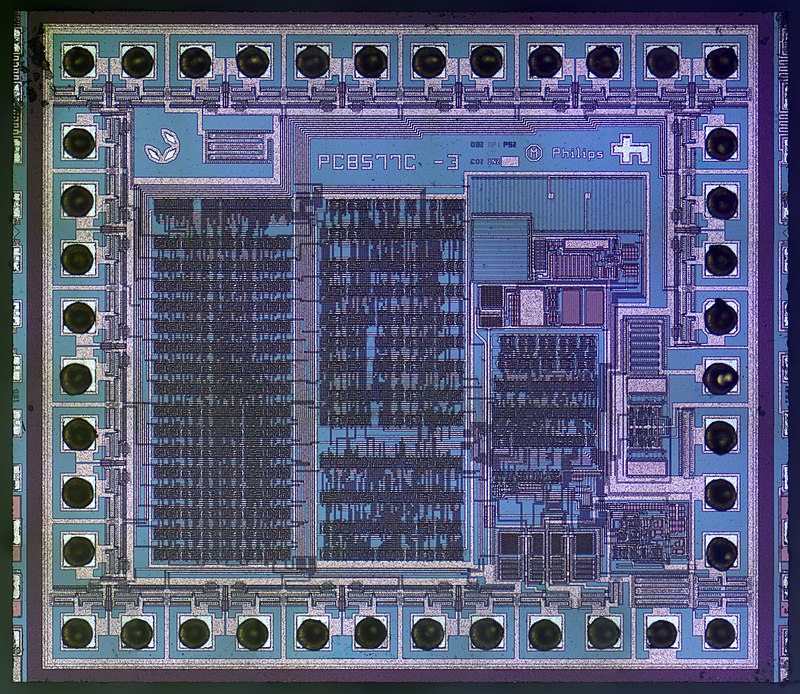

Integrated circuit - Wikipedia

Polymers in Electronic Packaging: Build-Up Films for Flip Chip Semiconductor Substrates, Part One - Polymer Innovation Blog

Application Notes

PDF) Semiconductor Packaging: Materials Interaction and Reliability

Kevin Zheng, Author at Circuit Artists

Beyond the 100 Gbaud directly modulated laser for short reach applications

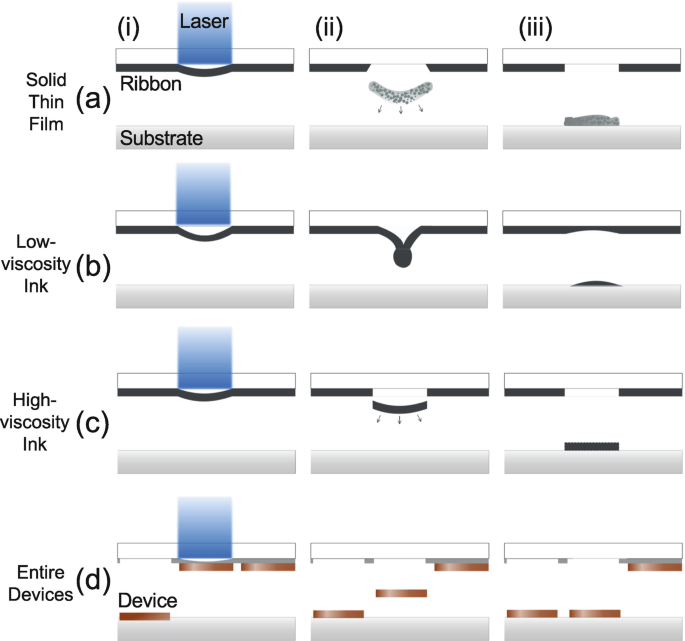

Laser-Induced Forward Transfer Applications in Micro-engineering

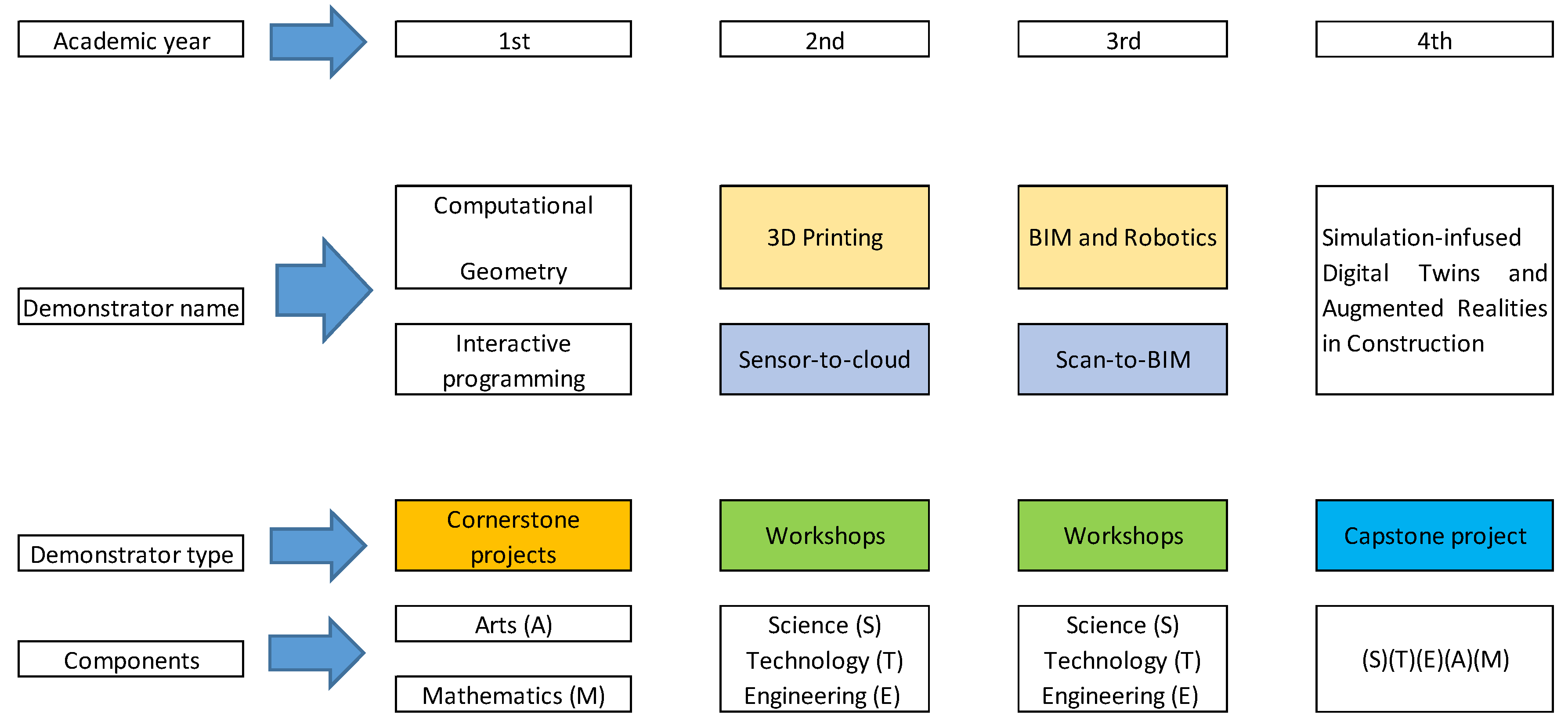

Buildings, Free Full-Text

AI/ML algorithms and applications in VLSI design and technology - ScienceDirect

How to design a circuit from scratch - Quora

Electronics, Free Full-Text

Flip-Chip BGA: PCB Layout Best Practices - Free Online PCB CAD Library